# IEEE UKRAINE SECTION IGOR SIKORSKY KYIV POLYTECHNIC INSTITUTE

## 2022 IEEE 41<sup>th</sup> INTERNATIONAL CONFERENCE ON ELECTRONICS AND NANOTECHNOLOGY (ELNANO)

## CONFERENCE PROCEEDINGS

OCTOBER 10-14, 2022 KYIV, UKRAINE

## 2022 IEEE 41th International Conference on ELECTRONICS AND NANOTECHNOLOGY (ELNANO)

Copyright © 2022 by the Institute of Electrical and Electronics Engineers, Inc.

All rights reserved.

#### Copyright and Reprint Permission Copyright and Reprint Permission:

Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. For reprint or republication permission, email to IEEE Copyrights Manager at <a href="mailto:pubspermissions@ieee.org">pubspermissions@ieee.org</a>.

All rights reserved. Copyright@2022 by IEEE.

IEEE Catalog Number: CFP2205U-USB

ISBN: 978-1-6654-6921-0

Organizing Committee of IEEE ELNANO-2022 E-mail: elnano@ieee.org.ua Faculty of Electronics, Igor Sikorsky Kyiv Polytechnic Institute Politekhnichna Street 16/9, Block #12, off. 423, 03056, Kyiv, Ukraine ELNANO-2022 Program Committee

#### Program Committee

Oleksii Bogdanov National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Juliy Boiko KNU

Oleksandr Bondarenko National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Tetyana Borodinova F. D. Ovcharenko Institute of Biocolloid Chemistry, NAS of

Ukraine

Viktor Bovtun Institute of Physics ASCR

Igor Boyko Ternopil Ivan Puluj National Technical University

Vladimir Burlaka State Higher Educational Institution "Priazovskyi State Tech-

nical University"

Artem Chernov National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Yuriy Didenko National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Sergii Dukhopelnykov IRE

Oleksandr Fedorchuk V.I. Vernadsky Institute of General and inorganic chemistry

of the National Academy of Sciences of Ukraine Ukrainian State University of Chemical Engineering

Liliya Frolova Ukrainian State University of Chemica Vitaliy Gargin Kharkiv National Medical University

Irina Golubeva National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Oksana Harmash National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Pavlo Herasymenko Institute of Electrodynamics of NASU Volodymyr Hnatushenko Dnipro University of Technology

Arsenii Ievtushenko Institute for problem of material science, NASU

Kateryna Ivanko Electronic Engineering Department, Faculty of Electronics,

Igor Sikorsky Kyiv Polytechnic Institute

Nataliia Ivanushkina National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Yevgeniy Karplyuk National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Victor Kazmirenko National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Tetyana Khyzhnyak National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Konstantin Kolisnyk National technical university "Kharkiv polytechnic institute" Lyubomyr Korolevych National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Dmitri Koroliouk Institute of telecommunications and global information space

of Ukrainian Academy of Sciences

Ievgen Korotkyi Department of Design of Electronic Digital Equipment, Na-

tional Technical University of Ukraine "Kyiv Polytechnic In-

stitute"

ELNANO-2022 Program Committee

Anton Koval Luleå University of Technology, Department of Computer Sci-

ence, Electrical and Space Engineering

Victoria Koval National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

V.I. Kubov ChDU

Ajay Kumar Jaypee Institute of Information Technology

Lyudmyla Kuzmych National Aviation University

Denys Lebedev National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Vladyslav Lisnyak Chemical Department, Kyiv National Taras Shevchenko Uni-

versity.

Borys Lupyna National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Eduard Lysenkov Petro Mohyla Black Sea National University

Oleksandr Machulianskyi National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Jaya Madan Chitkara University Institute of Engineering and Technology,

Chitkara University.

Vazgen Melikyan Synopsys Armenia CJSC

Igor Melnik National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Oleksandra Miroshnychenko Teleoptic PRC, ltd

Vitalii Mokin Vinnytsia National Technical University

Dmytro Mykolaiets National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Sergey Naida National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Serhii Nedilko Taras Shevchenko National University of Kyiv

Igor Nesteruk Institute of Hydromechanics, National Academy of sciences of

Ukraine

Stepan Nichkalo Lviv Polytechnic National University

Nikolay Nikolov National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Alexander Nosich IRE NASU

Ivan Ostroumov

Tetyana Obukhova National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Ostap Oliinyk National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Valery Oliynik Institute of Hydromechanics of NASU

Anatolii Orlov National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Sergey N. Osinov National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute" National Aviation University

Kateryna Osypenko National Technical University of Ukraine "Igor Sikorsky Kyiv

Polytechnic Institute"

Volodymyr Palahin Cherkasy State Technological University

ELNANO-2022 Table of Contents

| Analysis and Processing of Acoustic Emission Signals Under Dynamic Loading of the Microstructure of Continuous Media                        |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Efficiency Analysis of DC-DC Converter with Pulse-Width and Pulse-Frequency Modulation                                                      |

| Using RSSI Data for LoRa Network Path Loss Modeling                                                                                         |

| Some Properties of Optically Excited Semiconductors under the Surface Wave of<br>mm-Wave Band Acting                                        |

| Reference voltage source optimization                                                                                                       |

| Metallic Cylindrical Resonator Vibratory Gyroscope Sensitivity to Random Vibration 590<br>Sergii Golovach and Valeri Chikovani              |

| Simulation of the Influence of Non - Gaussian Noise During Measurement                                                                      |

| Doppler (HF) Radar Facility for Monitoring Dynamic Processes in Geospace                                                                    |

| Multifrequency Doppler Software-Controlled Receiving System for Space Weather  Monitoring                                                   |

| Features of Physical Processes Which Flow in Planar Systems of Cylindrical Piezoceramic Radiators with Internal Acoustic Screens            |

| On the Influence of the Acoustic Interaction of Cylindrical Piezoceramic Radiators in<br>Planar Systems on their Physical Fields            |

| On the Impact of the Physical Properties of Piezoceramic Materials on the Mechanical<br>Fields of Cylindrical Radiators of Screened Systems |

| Modular Residential Power Supply With Renewable Sources, Zero Export Capability<br>and Active Harmonic Filtering                            |

| Increasing Performance of Cooling Systems for Radar Transmit/Receive Modules                                                                |

## Reference Voltage Source Optimization

Leonid Pavlov

The department of design of electronic digital equipment,

Faculty of Electronics

Igor Sikorsky Kyiv polytechnic institute

Kyiv, Ukraine

leonpavl@gmail.com

Abstract- The article shows the possibility of reducing the temperature coefficient for the reference voltage source (RVS), built on bipolar transistors. In the first step is offered the structural scheme with compensators of decrease in temperature characteristics. The second step is to generate additional voltage to compensate for the nonlinearity of the temperature characteristic. The next step is to develop a circuit of an electrical type compensator and an example of including one and two compensators in an uncompensated circuit. It also determines the rule for the use of subsequent compensators, if necessary. The parametric optimization of the offered examples of RVS is carried out. An experimental study of the example of RVS with one link of compensation was also conducted. As a result of optimization, the value of temperature instability was reduced from 4.4 mV in the basic circuit to 1.2 mV for one compensator, and to 0.515 mV for the case of two compensators, which proves the effectiveness of the proposed strategy and

Keywords — reference voltage source; bipolar technology; temperature dependence; temperature coefficient; structural optimization; parametric optimization

#### I. INTRODUCTION

The topic of this work concerns the class of reference voltage sources, which are based on the theoretical principles of the band gap. Such RVS occupy a special place as an independent integrated circuit and an important block in a significant list of integrated circuit nomenclature: analog-to-digital and digital-to-analog converters, secondary power supplies, DC / DC converters, etc. The architecture of these RVSs usually contains a voltage source proportional to the absolute temperature (PTAT) and a voltage source inversely proportional to the absolute temperature (CTAT). These PTAT and CTAT sources usually compensate for each other to obtain a constant output voltage at only one point in the temperature range. When the temperature deviates from the design point, there is a deviation of the reference voltage, which increases with temperature deviation.

#### II. STATEMENT OF THE PROBLEM AND ANALYSIS SOLUTIONS

The purpose of the work in accordance with the current trend is to reduce the nonlinearity of the temperature characteristics of RVS.

It is also necessary to formalize the process of minimizing the nonlinearity of the temperature characteristic to narrow the limits of instability of the original RVS.

Accordingly, perform parametric optimization according to the selected criteria for the best choice of component parameters.

#### III. ANALYSIS OF RECENT ACHIEVEMENTS

To reduce temperature instability, modern approaches use different approaches to reduce temperature dependence. Denys Lebedev

The department of design of electronic digital equipment,

Faculty of Electronics

Igor Sikorsky Kyiv polytechnic institute

Kyiv, Ukraine

d.lebedev@kpi.ua

In work [1], a precision reference voltage source (PRVS) was proposed, which is made by CMON technology, according to the block diagram shown in Fig.1.

Fig. 1. Precision reference voltage source

The parameter  $\gamma$  in this paper is called the mobility temperature exponent. The threshold voltage extractor is based on a control MOS transistor in which the gate is connected to the drain, its coil is grounded and the current sources entering the coil.

In works [2-4] precision sources of reference voltage are offered, which are also made by CMOS technology according to the calculation scheme shown in Fig.2.

Fig. 2. Reference voltage source circuit

The paper [4] also lists the calculation scheme. This allows you to effectively adapt the results to variations in the technological process of manufacturing RVS. According to the calculations in [2], the temperature coefficient was reduced to 5.5 ppm/°C in the temperature range –45... +85 °C. When operating the circuit at a temperature of 27 °C, the output voltage of the RVS was 1.207 V. The result was achieved by adding to the core of the RVS source currents that depend on the threshold voltage of the MOS transistors.

In [5], a transistor gain compensation scheme was used to construct the RVS, which allowed to eliminate the error introduced by the bipolar transistor base current. Together with the logarithmic compensation scheme, it was possible to achieve a temperature coefficient of 3.3 ppm / °C in the temperature range from -45 to + 125 °C.

In work [6], the authors abandoned bipolar transistors in the structure of the RVS core. Therefore, the PTAT and CTAT voltages are generated exclusively by MOS transistors, which are in the mode of weak inversion, i.e. in the subthreshold region. The results of calculations provided by the authors of [6] show an error of about 1.2 mV in the temperature range -40... 100 °C, which is 24 ppm/°C for the output voltage RVS 451.69 mV from the minimum voltage of the power supply of 0.6 V with a total variation of 1.34 mV.

The structure of RVS based on CMOS transistors, where the core is also built on MOS transistors, which are in the mode of weak inversion, is provided in [7-8]. In them, the authors cite analytical dependences of the output voltage of the RVS on the parameters of the MOS transistors. The measurement results of the three plates are given in [7]. show an error of  $3\sigma\pm1.0\%$  when changing the temperature from 0  $^{\circ}$  C to 100  $^{\circ}$  C The proposed solution provides an average reference voltage of 1.245 V at a sensitivity of 0.31% /V and a deviation of the power supply of -41 dB, consuming 35 pW from 1, 4 V at room temperature. In [8], the calculations showed the value of the temperature coefficient not more than 2 ppm /  $^{\circ}$ C in a narrow temperature range of 100  $^{\circ}$ C. And this is another argument in favor of dividing the operating temperature range.

RVS, which is powered by radio radiation, is presented in [9]. RVS consumes only 22 μA at an output voltage of 485.8 mV and has a deviation of 7 ppm / °C in the temperature range from—10 to 70 °C. As in previous works [6-8], the circuit is made exclusively on CMOS transistors.

Proposed in [10], as in [2], the method of designing RVS, divides the temperature range into two parts: the left part - the temperature range below the set point, and the right - the area of higher temperatures. The working area is considered as a temperature range from -40 to + 100 °C. The implementation is similar to the scheme shown in Fig.2. and provides 1% accuracy in the specified temperature range from -40 to + 100 °C.

The purpose of [11] is to reduce the noise level in the RVS with a supply voltage of ± 5V. Chopper stabilization (modulator-demodulator) is used for this purpose. The temperature coefficient was experimentally confirmed at 148 ppm / °C in the temperature range from -40 °C to 85 °C, which satisfies the design task. The reference voltage consumption is 15.65 mW. The spectrum of low-frequency output noise can reach -140 dBV / √ Hz. The optimization of RVS according to the criterion of minimum noise in the region of 100 Hz is also performed in the work.

In work [12], the RVS core is made according to the scheme of Fig.2. In this publication, an analysis of the discrepancy between the parameters of the denominations of the elements and the error of their manufacture by the Monte Carlo method. Optimization of RVS according to the criterion of the minimum area of the crystal is performed.

In work [13], the analytical dependence of the output voltage of the RVS, which is based on CMOS transistors, on temperature is also given, and the circuit is optimized according to several weighted criteria. The main emphasis is on the minimum linear sensitivity of the output voltage.

A grid optimization method of RVS was proposed in work [14], the core of which is made according to the scheme of Fig. 2, with a complex criterion of optimality, which takes into account both the electrical characteristics of the device and the crystal area. The most important characteristic is the noise density, which is calculated at the optimal point was  $7\mu V$  /  $\sqrt{Hz}$ .

A new method of dynamic optimization of the reference voltage was proposed in [15]. The criterion of optimality is presented in analytical form in such a way that it is possible to organize calculations in parallel processes. But examples of implementation of this method for the design of RVS on the crystal in this paper are not given.

The method of optimization of RVS on the basis of analytical relations at the level of impurity distribution is given in [16]. Indirectly, the work emphasizes the relevance of RVS on bipolar structures.

The content of the article [17] is devoted to structural and parametric optimization of RVS. The optimization process was aimed at minimizing the power consumed by RVS and the crystal area. As a result, RVS on FINFET structures had a power consumption twice as low as RVS on MOSFET structures.

As a result of the review of the best new achievements it is possible to note that;

- Basically, the specifics of these approaches are largely based on the achievements of modern CMOS technology.

- Due to the design of the RVS core based on CMOS structures, it was possible to halve the supply voltage and the output voltage of the RVS.

- 3) Due to the construction of the RVS structure on the basis of both bipolar and MES transistors, it is possible to achieve better compensation for temperature instability than on structures of a single type: only bipolar, or only MOS transistors.

The vast majority of achievements have a clear bias towards the design based on CMOS technology due to the desire to reduce power consumption and output voltage RVS. The best of the studied projects [1] showed a variation of the output voltage of 3.3 ppm/°C in the temperature range of 160 °C from -45 to + 125 °C. Interestingly, when narrowing the operating temperature to 100 °C, it is possible to reduce the temperature coefficient to 2 ppm/°C [8]. But in the field of implementations on bipolar structures, activity is not noted in the publications.

It is worth noting that the well-known Brocau circuit, which was developed on bipolar transistors decades ago, has a temperature coefficient of 5 ppm / ° C for the maximum temperature range (military temperature range). Thus, it gives reason to believe that the issue of improving the temperature coefficient is a problem that needs to be solved, and the search may be in the direction of implementations on bipolar structures.

The analysis of the best achievements also shows that the problem of reference voltage sources based on CMOS technology is the difficulty of working in a wide range of temperatures. When the conditions of ionizing radiation are added, it becomes clear that bipolar structures still remain highly competitive for the design of universal sources of reference voltage, as evidenced by the latest research presented in the dissertation [18].

Thus, the direction of research of this work is to reduce the temperature coefficient of RVS, made on the basis of structures of bipolar transistors.

#### IV. STRUCTURAL AND PARAMETRIC OPTIMIZATION

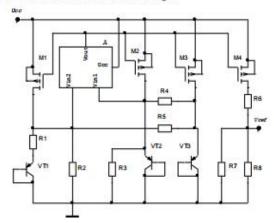

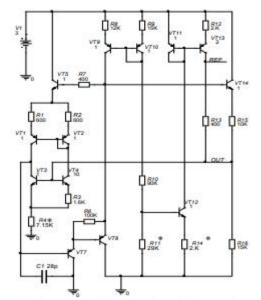

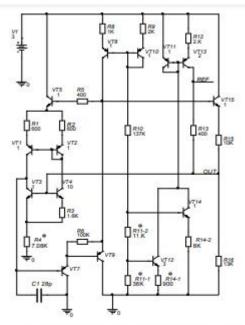

Consider the typical structure of RVS on bipolar transistors, Fig.3.

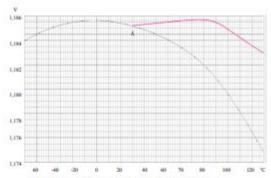

It is proved [19] when RVS is the part of an integrated circuit, the accuracy of the temperature dependence under the symmetrical setting shown in Fig. 4 depends little on whether the circuit resistors are film or based on basic diffusion.

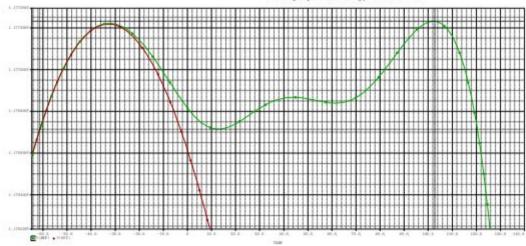

The maximum deviation from the set point determined by the above nominal value R4 at 20  $^{\circ}$ C is 4.4 mV. In the temperature range from -60 to +140  $^{\circ}$ C.

Structural optimization is introduced into the block diagram of compensators of nonlinearity of temperature dependence in the selected operating range. Therefore, the block diagram of the RVS must include compensators operating in a given temperature range relative to the set point. Thus, the structural scheme consist from: REF Core, Compensators from 1 to N and total output.

#### V. COMPENSATION STRATEGIES

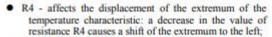

First, let's limit the circuit to only one compensator. Then the optimization strategy may be to shift the temperature characteristic to the left, fig. 5 solid line, and raise the right side of the temperature characteristic compensator, red line.

You need to add a compensator to the base circuit so that it turns on at the beginning of the red line and adds voltage at the new exit point. A possible option for such an optimization of the circuit is to adjust the output voltage of the RVS due to the additional voltage on the resistor, which acts as a current-

Fig. 3. Basic scheme of RVS.

Fig. 4. Temperature dependence of RVS according to the scheme of Fig.3

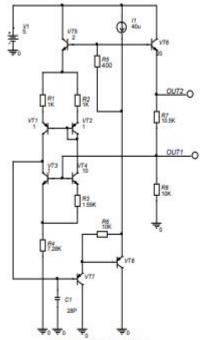

voltage converter. Then the contact of the of the resistor, where the additional voltage is formed, becomes a new generator, which will turn on with increasing temperature at point A, Fig. 5. Such a model of RVS, which solves this problem, is shown in Fig. 6.

The optimization criterion in this case is the minimum width of the area of variation of the output voltage RVS, i.e. the minimum deviation of the maximum value of the maximum value of the output voltage RVS in the temperature range.

The target function is formed as the sum of the squares of the deviation from the average value of the RVS voltage at the temperature control points: -60, -40, -20, ..., 120 °C. The target function also takes into account the restrictions on the maximum and minimum values of the resistance of the resistors and the minimum emitter-collector voltages of the transistors at which the saturation mode of the transistor occurs.

The search algorithm provides a minimum scheme: the maximum component of the vector of the objective function is minimized. The search method is of zero order according to the Hooke-Jeeves scheme.

Variables of optimization are defined by the preliminary analysis of the scheme, which has defined the most sensitive elements of the scheme to the chosen strategy:

Fig. 5. Strategy for correcting temperature dependence

Fig. 6. RVS scheme as a model with one-stage adjustment of temperature dependence

- R11 affects the initial temperature of the compensator current generator on the transistor VT12 with a single area of the emitter: a decrease in resistance shifts the beginning of the current generation in the region of higher temperatures;

- R13 voltage resistor, determines the scale of the voltage applied to the voltage of the base circuit;

- R14 affects the amount of current and the slope of the volt-ampere characteristic of the current generator: increasing the value of resistance reduces the current of the generator.

#### Restrictions include:

- The emitter-collector voltage of any circuit transistor must be greater than 0.45 V.

- Nominal values of resistors R4, R11 and R14 should be within 1.0... 120 kΩ and take quantized values in the form of not more than three bits. For example, nominal value of 12.1 kΩ is permissible, and a value of 12.12 kΩis the excess of the accuracy of the bit grid.

The initial conditions were determined by the value of the resistor R12, which determines the level of current reflected in the resistor of the voltage boost R13.

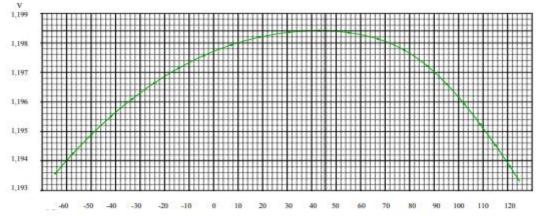

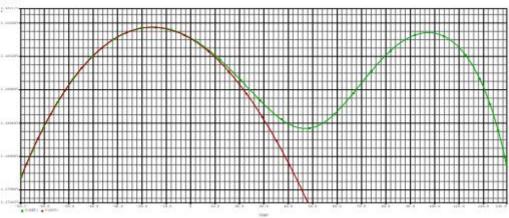

As a result of optimization, a temperature characteristic compensated to 1.15 mV in the temperature range from -60 to 125.5 °C, which is 7.7 ppm/°C, Fig.7. This is almost three times better than in the basic scheme.

Further reduction of the deviation of the temperature characteristic in the temperature range is possible when building the second model RVS under the condition of further shift to the left of the temperature dependence and the addition of another compensator, as shown in Fig.8.

Fig. 7. Temperature dependences on the outputs OUT of the base (red) and REF compensated (green) part of the circuit

Fig. 8. RVS model with double adjustment of temperature dependence

As can be seen from Fig.8, the principle of connecting an additional compensator is not difficult. It is enough to add a resistor in the base-emitter circuit and to connect another current generator to the current mirror made on transistors VT11, VT13. In this case, its role is performed by the transistor VT12, which begins to operate after the voltage at the base-emitter junction reaches a significant value. In this model, the first to turn on the current generator on the transistor VT14 and only with a further increase in the connection temperature of the generator on the transistor VT12. The collectors of transistors VT12 and VT14 are connected. As the result their currents are reflected and through the collector of transistor VT13 enters the resistor R13, which releases the voltage to compensate for the error of temperature dependence.

The optimization criterion, the principle of constructing the objective function, the method of finding the optimal point and constraints remained the same as for the single-stage compensation model.

R4, R11-1, R11-2 and R14-1, which are marked with an asterisk, act as optimization variables from the previous scheme. R10 and R14-2 were added to the thread. The nominal values of the resistors in Fig.9 are for the optimal point, and the temperature dependence is shown in Fig.10. The amplitude range of the output voltage is 515 μV in the temperature range from -60 to 120 °C. This is 8.5 times better than the original baseline. This fully proves the effectiveness of the proposed strategy and models.

Fig. 9. Temperature dependence in the model with two compensators

#### VI. TESTING MODELS

Experimental tests were performed for the single compensator variant only. The conditions of the test allowed to ensure an accuracy of 1.1%. Within the specified accuracy, the results of the study coincided with the above calculations.

#### VII. CONCLUSIONS

- Strategies and models of compensation of nonlinearity of temperature characteristic of RVS are offered.

- The reduction of the value of temperature instability from 4.4 mV in the basic scheme to 1.2 mV for one

- compensator, and 0.515 mV for the case of two compensators, which proves the effectiveness of the proposed strategy and models.

- Implementation examples with one and two compensating links are proposed. By analogy, as many elements are introduced as needed to improve the accuracy of the reference voltage source.

- A criterion for the structural and parametric optimization of the initial circuit is proposed and the result obtained is 4 times better than the original circuit.

#### REFERENCES

- A high precision logarithmic-curvature compensated all CMOS voltage reference (2018). //Nejad T.G., Farshidi E., Sjoland H., Kosarian A. Springer Nature 2018, Analog Integrated Circuits and Signal Processing. https://doi.org/10.1007/s10470-018-1296-0

- [2] Jin S., Li Z., Li J., Wang A. A Low Power Bandgap Voltage Reference with Nonlinear Voltage Curvature Compensation. DESteeh Transactions on Engineering and Technology Research · April 2017. https://doi.org/10.12783/dtetr/iceta2016/7042

- [3] Schaeffer P. L. A Simple Sub-IV Voltage Reference. Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of Master of Science in Engineering. - The University of Texas at Austin, December 2017. https://repositories.lib.utexas.edu/handle/2152/68219

- [4] Calvillo J. F.P. (2016). Design of Bandgap Voltage Reference with Curvature Compensation for the Space Industry. (2016). Thesis to obtain the Master of Science Degree in Electronics Engineering. October 2016. 9 pp.

- [5] A Precision Voltage Reference Circuit with Trimming for 16-bit SAR ADC in 55nm CMOS Technology (2018)/ Wang H., Wang J, Su J., Zhang G., Liang F. Proceedings of the 2018 3rd International Conference on Integrated Circuits and Microsystems. 2018 IEEE, pp. 94-97.

- [6] Madeira R., Paulino N. (2017) Design Methodology for an All CMOS Bandgap Voltage Reference Circuit. 8th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), May 2017, Costa de Caparica, Portugal. pp.439-446. https://doi.org/10.1007/978-3-319-56077-9\_45hal-01629561

- [7] Lee L, Sylvester D., Blanuw D. (2017). A Subthreshold Voltage Reference With Scalable Output Voltage for Low-Power IoT Systems. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 52, NO. 5, MAY 2017, pp.1443-1449.

- [8] Yin Y. Performance characteristics and design of voltage. References/ (2017). Iowa State University. Graduate Theses and Dissertations. 17370. – 69 pp. https://lib.dr.iastate.edu/etd/17370

- [9] Design of low-power voltage/current references and supply voltage for 9-bit fully differential ADC. (2016)/ Bako N., Broz I., Butković Z., Magerl M., Barić A. https://doi.org/10.7305/automatika.2016.03.1616

- [10] Design Techniques for Low-Power and Low-Voltage Bandgaps/ (2021). Barteselli E., Sant L., Gaggl R., Baschirotto A. Electricity 2021, 2, 271–284. https://doi.org/10.3390/electricity2030016

- [11] Lingjie P., Xiangliang J., Mengliang L. (2017). Design and Optimization of a Low-Noise Voltage Reference Using Chopper Stabilization Technique Chinese Journal of Electronics, Vol.26, No.5, Sept. 2017.

- [12] Andrade A., Petraglia A., Soares C. (2017). A constrained optimization approach for accurate and area efficient bandgap reference design. Microelectronics Journal 65 (2017) 72–77. http://dx.doi.org/10.1016/j.meju.2017.03.012

- [13] Performance optimization for the CMOS voltage reference circuit based on NSGA-II. (2018). // Huang H., Zeng Y., Chen R., Tan H. 2018 IEEE Asia Pacific Conference on Circuits and Systems. Pp. 82-85

- [14] Khalil K., Soliman, N. Omran H.( 2019). Automation of Bandgap Voltage Reference Optimization using Vectorized Coarse-Fine Grid Search. 2019 7th International Japan-Africa Conference on Electronics, Communications, and Computations, (JAC-ECC). – pp 54-57. DOI:10.1109/JAC-ECC48896.2019.9051334

- [15] Dynamic Optimization of SVR Control Parameters for Improving Tap Operation Efficiency of Voltage Control in Distribution Networks./ Murakami K, and ath. IEEJ TRANSACTIONS ON ELECTRICAL AND ELECTRONIC ENGINEERING. – pp. 1-11. https://doi.org/10.1002/tec.23269

- [16] Pankrat E.L. An Approach to Optimize of Manufacturing of a Voltage Reference Based on Heterostrucures to Increase Density of Their Elements. Analysis of Influence of Miss-Match Induced Stress and Porosity of Materials on Technological Process. - International Journal of Advance Robotics & Expert Systems (JARES) Vol.1, No.2, pp.41-60. https://airccse.com/jares/papers/1218jares/06.pdf

- [17] Meshram S., Panwar U., Optimization of Low Power CMOS based Voltage Reference Generator in 32nm. International Journal of Advanced Research in Computer and Communication Engineering, Vol. 7, Issue 8, August 2018 pp. 47-51. https://doi.org/10.17148/IJARCCE.2018.7810

- [18] Analysis of Bipolar Integrated Circuit Degradation Mechanisms Against Combined TID-DD Effects // Rudy Ferraro, Rubén García Alia, Member, IEEE, Salvatore Danzeca, and Alessandro Masi.

- [19] Borisov A. V., Pavlov L. N. Modification of the reference voltage source// Electronics and communication. - 2013. - No 4. - s. 14-20. http://nbuv.gov.ua/UJRN/eisv\_2013\_4\_4

2022 IEEE 41st International Conference on Electronics and Nanotechnology (ELNANO)